# An Integrated Subharmonic Coupled-Oscillator Scheme for a 60-GHz Phased-Array Transmitter

James F. Buckwalter, Member, IEEE, Aydin Babakhani, Student Member, IEEE, Abbas Komijani, Member, IEEE, and Ali Hajimiri, Member, IEEE

Abstract—This paper describes the design of an integrated coupled-oscillator array in SiGe for millimeter-wave applications. The design focuses on a scalable radio architecture where multiple dies are tiled to form larger arrays. A  $2 \times 2$  oscillator array for a 60-GHz transmitter is fabricated with integrated power amplifiers and on-chip antennas. To lock between multiple dies, an injection-locking scheme appropriate for wire-bond interconnects is described. The  $2 \times 2$  array demonstrates a 200 –MHz locking range and  $1 \times 4$  array formed by two adjacent chips has a 60-MHz locking range. The phase noise of the coupled oscillators is below –100 dBc/Hz at a 1-MHz offset when locked to an external reference. To the best of the authors' knowledge, this is the highest frequency demonstration of coupled oscillators fabricated in a conventional silicon integrated-circuit process.

Index Terms—BiCMOS integrated circuits, coupled oscillator, mutual injection locking, phased arrays.

## I. INTRODUCTION

UNLICENSED operation in the 59–64-GHz band is stimulating novel radio architectures for millimeter-wave integrated circuits. The available bandwidth offers gigabit/second data rates, and high absorption at 60 GHz is an important feature for dense networking. Transceiver circuits that operate at millimeter-wave frequencies have been demonstrated in silicon germanium (SiGe) fabrication technologies [1]–[3]. However, the integration of a complete phased-array transceiver with antennas on a single chip offers new design choices and opportunities [2]. Phased-array designs at the 24-GHz industrial-scientific-medical (ISM) band have demonstrated new receiver circuit architectures [4]–[9]. This paper demonstrates the application of a new circuit approach based on coupled-oscillator arrays for millimeter-wave phased-array designs in a standard SiGe integrated-circuit technology.

To maintain phase coherence between phased-array elements, oscillators on different dies must be phase locked. While coupled phase-locked loop architectures can maintain the phase relationship between neighboring oscillators [7], [8], coupled oscillators are well suited for fully integrated phased-array circuits. The wavelength at 60 GHz allows for several array

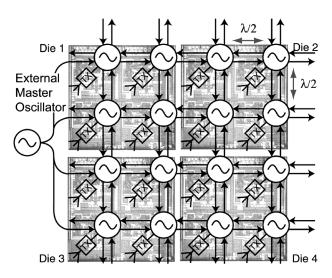

Fig. 1. Coupled-oscillator scheme for fully integrated phased-array transmitter. Each oscillator drives a transmit chain with a DAC controlled phase shifter, power amplifier, and antenna.

elements to be located on a single die. Consequently, an oscillator can be placed on each die or at each transmit element. One particular advantage of an on-chip coupled-oscillator array is the distribution of the carrier frequency between different transmit elements. Previous integrated phased-array implementations distribute 16 phases across the entire chip, results in large amounts of silicon area dedicated to wiring and high power consumption [4]. Global frequency distribution becomes increasingly difficult at millimeter frequencies. By co-locating an oscillator at each transmit stage, closer control of the delay mismatches between the local oscillator and the mixer stage is possible.

Scalable architectures are particularly appropriate for creating large phased arrays by tiling several dies. In Fig. 1, scalability is demonstrated for a phased-array transmitter. The phased array requires phase coherence between all elements. Since each chip requires frequency generation, neighboring chips are injection locked to ensure phase coherence. If oscillators are located at each antenna element, injection locking can lock the oscillators both on-chip and between chips. This tiling approach is useful not only for phased arrays, but also for applications where the separation between antennas might be several wavelengths. Consequently, this design approach focuses on an injection-locking scheme appropriate for an onand off-chip coupled-oscillator array.

In this transmitter implementation, a two element by two element  $(2 \times 2)$  array of transmitter cells is integrated on a single

Manuscript received March 28, 2006; revised August 23, 2006.

J. F. Buckwalter was with the Department of Electrical Engineering, California Institute of Technology, Pasadena, CA 91125 USA. He is now with the Department of Electrical and Computer Engineering, University of California at San Diego, La Jolla, CA 92093 USA (e-mail: buckwalter@ece.ucsd.edu).

A. Babakhani, A. Komijani, and A. Hajimiri are with the Department of Electrical Engineering, California Institute of Technology, Pasadena, CA 91125 USA (e-mail: aydin@caltech.edu; komijani@caltech.edu; hajimiri@caltech.edu).

chip with antennas. In [5], array scalability originally motivated investigation into a coupled-oscillator topology. This paper expands on the design details of the coupled-oscillator array by describing the interconnect structure for subharmonic injection locking, as well as the circuit implementation of the injectionlocked voltage-controlled oscillator (VCO). Additional results illustrate the circuit operation in the time domain. The measured results show that the phase noise of each element can be suppressed when locked to an external source across a single chip, as well as across two chips.

In Section II, we summarize the analysis of coupled oscillators and explain the motivation of using these circuits for fully integrated phased-array elements. In Section III, we discuss the circuit design of the coupled-oscillator cell and the coupling network. Finally, the results for the coupled-oscillator array are presented and compared to the performance of individual oscillators in Section IV.

## II. COUPLED OSCILLATORS

Adler described the unilateral locking phenomena in coupled oscillators [10] and Kurokawa later studied the microwave dynamics [11]. The basic phase relationship between neighboring oscillators is

$$\Delta \phi = \sin^{-1} \left( \frac{2Q}{\omega_o} \frac{I_{\rm osc}}{I_{\rm inj}} \Delta \omega \right) \tag{1}$$

where  $\Delta \phi = \phi_o - \phi_{inj}$  and  $\Delta \omega = \omega_o - \omega_{inj}$  are the phase difference and natural frequency detuning between the local oscillator and an injected signal,  $\omega_o$  is the carrier frequency, Q is the quality factor for the oscillator, and  $I_{osc}$  and  $I_{inj}$  are the oscillator and injection currents. The locking range is defined as twice  $\Delta \omega_m = \omega_o I_{inj}/2QI_{osc}$  and allows the phase difference to theoretically vary from  $-90^\circ$  to  $90^\circ$ . The frequency detuning relationship is demonstrated in [10]. Increasing the locking range is possible with increasing  $I_{inj}$  or decreasing  $I_{osc}$ . The passive components of the tank bound the oscillator Q and strongly affect the oscillator phase noise. From a testing standpoint, we use the injected current to control the locking range

Bilateral oscillator arrays were first proposed by Stephan [12]. York and Compton [13], York *et al.* [14], and York and Itoh [15] proposed coupled oscillators for electronic beam steering through injection at the periphery of the array. The effect of bilateral injection locking is to modify the behavior in (1). In this case, the phase dynamics of the array produce a linear phase gradient across the array. In [15], the dynamics for a coupled-oscillator array with bilateral and external injection locking for beam steering are described as

$$\frac{d\phi_i}{dt} = \Delta\omega_i - \frac{\omega_i}{2Q} \frac{I_{\text{osc}}}{I_{\text{inj}}} \left( \sin(\Delta\phi_i) - \sin(\Delta\phi_{i-1}) \right) \\ + \frac{\omega_i}{2Q} \frac{I_{\text{osc}}}{I_{\text{ext}}} \left( \sin(\Delta\phi_{\text{ext}}) - \sin(\Delta\phi_i) \right) \quad (2)$$

where  $\Delta \omega_i = \omega_i - \omega_{i+1}$  and  $\Delta \phi_i = \phi_i - \phi_{i+1}$  are the frequency detuning and phase difference between the *i*th and *i* + 1 oscillators, and  $I_{\text{ext}}$  and  $\phi_{\text{ext}}$  are the external injection current and phase, respectively. The continuum dynamics for beam steering have been studied by Pogorzelski *et al.* [16] and experimental

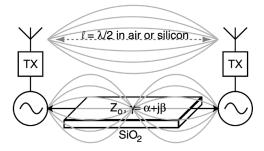

Fig. 2. Impact of different dielectric mediums for the interconnect scheme and the radiation network. The coupled oscillators will not necessarily be separated by half a wavelength at the subharmonic frequency. The coupled oscillator is connected by a transmission line with attenuation  $\alpha$  and propagation constant  $\beta$ . The impedance on the line is  $Z_{\rho}$ .

results have recently demonstrated the array pattern for oscillator arrays of discrete components [17].

In integrated circuit implementations, the process, voltage, and temperature (PVT) variations between different oscillators introduce phase errors between neighboring elements. For process variations, the design is subject to less variation across a single die than across different wafers. Therefore, the frequency range ensures the locking of the array must be greater when considering locking between different dies than locking between oscillators on a single die. Other characteristics of coupled-oscillator dynamics are worth consideration. First, the phase noise increases with the frequency detuning between neighboring oscillators [18]. Additionally, the phase noise limits the allowable frequency detuning. As the edges of the locking range are approached, the oscillators can lose lock. For this reason, coupled-oscillator arrays have found a limited role in beamsteering since  $+/-60^{\circ}$  is necessary between array elements for beamforming. Secondly, stability analysis of coupled-oscillator dynamics demonstrates the possibility of unwanted modes in large arrays [19], [20].

Instead of exploiting the phase relationships in (1) and (2) to control the beam angle, this study instead relies on injection locking solely as a means to distribute and phase lock the carrier signal across a single chip and between neighboring chips. The locking range consequently must be large enough to satisfy the PVT variations in a particular integrated-circuit technology. Slight supply variations shift the natural frequencies of neighboring oscillators, as will be demonstrated in Section IV. The relative phase control of each transmit stage is independently provided with digital-to-analog (DAC) controlled mixers for beamforming and data modulation. This circumvents many of the problems of relying on coupled-oscillator dynamics for beamsteering.

Finally, we consider the coupled-oscillator network as it applies to the phased-array transmitter. The distance between neighboring oscillators that are co-located with the antenna is dictated by the half-wavelength spacing in air or, if a silicon lens is used to focus the antenna pattern, in silicon [2]. This is illustrated in Fig. 2. One of the advantages of using a silicon lens is that the distance between array elements will be much shorter since silicon has a dielectric constant of 11.9. However, the coupling network in a standard silicon process will be located in the metal stack and, consequently, propagate through a different dielectric, i.e., silicon dioxide. It is interesting to consider the number of wavelengths of the Mth subharmonic of the oscillator frequency that separate the neighboring elements

$$n_{\lambda,\text{interconnect}} = \frac{1}{2M} \sqrt{\frac{\varepsilon_{\text{SiO}_2}}{\varepsilon_{\text{rad}}}}$$

(3)

where  $\varepsilon$  is the dielectric constant of the silicon dioxide and the radiating medium. M could be chosen to minimize the attenuation over the interconnect. The choice of the subharmonic frequency will be discussed in Section III. Notably, if the first subharmonic is used (M = 2) and the radiative dielectric is air, the interconnect will be approximately one-half of the subharmonic wavelength. However, if the radiative dielectric constant is instead silicon, the interconnect length is reduced to 0.14 of the subharmonic wavelength. By matching the impedance of the oscillator source to the coupling interconnect, the impact of the propagation constant is primarily reduced to the role of attenuation on the coupling signal.

One final consideration regarding the use of coupled-oscillator arrays for beamsteering applications involves the phase jitter of each oscillator. Ideally, neighboring oscillators should have identical phases, but the phase noise of each oscillator is independent and the limited injection-locking bandwidth between oscillators causes a statistical variation, known as phase jitter, that corrupts the mean phase between the neighboring oscillators. The cycle-to-cycle phase jitter between two oscillators can be expressed as

$$\overline{\Delta\theta(\tau)}^2 = \frac{16}{\omega_o^2} \int_0^\infty S_\theta(f) \left(\sin(\pi f \tau)\right)^2 df \tag{4}$$

where  $S_{\theta}(f)$  is the power spectrum of the phase of each oscillator and is assumed to be identical for both oscillators. In many cases, the power spectrum of the phase can be estimated from the measured phase noise  $L[\Delta \omega]$ . Consequently, the phase noise of each oscillator must be suppressed sufficiently through injection locking to minimize the phase error between neighboring elements. Any contribution to the phase jitter will degrade the beam pattern and induce an error vector for data communication.

## III. SCALABLE TWO-DIMENSIONAL (2-D) COUPLED-OSCILLATOR ARRAYS

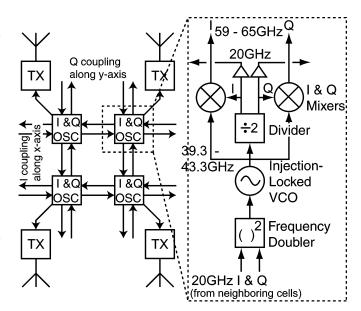

The basic coupled-oscillator topology is shown in Fig. 3. The  $2 \times 2$  phased array contains four oscillators at each transmit (TX) stage. The block diagram demonstrates the implementation of the oscillator cell. Each oscillator is designed to operate at 40 GHz. Isolating the oscillator from the power amplifier and antenna is critical because on-chip coupling is difficult to accurately model and severely degrades performance through pulling between the oscillator and power amplifier [21]. By shifting the oscillator frequency to 40 GHz, the unwanted coupling is reduced. The oscillator is divided to 20 GHz and mixed with the 40-GHz signal to achieve the 60-GHz in-phase (I) and quadrature (Q) components.

Fig. 3. Coupled-oscillator schematic. The oscillators are coupled along two dimensions. The coupling network operates at one-third the carrier frequency.

#### A. Interconnections

Coupling between different dies requires considering the interconnect. If wire bonds are used to provide the interconnect between two dies, frequencies above 20 GHz are strongly attenuated through poor matching and reflections. These losses reduce the injected current strength between the neighboring dies and weaken the locking range described in (2). Tiling chips at half-wavelength spacings keeps the inter-chip spacing small  $(< 200 \ \mu m)$  and minimizes the wire-bond inductance. Consequently, we choose to injection lock at a subharmonic of the local oscillator frequency. The first subharmonic at 20 GHz is available from the carrier generation scheme described above and illustrated in Fig. 3. Since the static dividers provide I and Q signals, we propose an I/Q scheme for coupling within a 2-D array of oscillators. In Fig. 3, the 20-GHz I signal is coupled along the x-axis while the Q signal is coupled along the y-axis. Consequently, each oscillator in the integrated  $2 \times 2$  array receives an I and Q subharmonic signal from its neighbors.

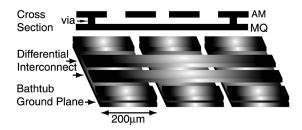

Coupled oscillators can simplify the distribution of high-frequency carrier energy over a phased array. However, electromagnetic simulations indicate the on-chip antenna will radiate substantially within the silicon substrate and silicon-dioxide metal stack since the dielectric constant of silicon is much higher than air [2]. The presence of a global transmission line interconnect grid absorbs part of this radiated energy. The transmission-line structure for the coupling interconnects was modified to reduce the absorption of radiated energy. The interconnect transmission line is illustrated in Fig. 4. The ground plane is a bathtub, which shields the differential interconnects from the substrate similar to the transmission lines described in earlier microwave and millimeter-wave designs [22], [23]. The bathtub ground plane, however, is severed every 200  $\mu$ m to avoid the absorption of radiated millimeter-wave energy. The differential coupling signal travelling in the transmission line is relatively unaffected by the severed ground plane since the return currents in this structure are localized. IE3D simulations

Fig. 4. Interconnect structure with severed bathtub to prevent coupling to integrated antenna.

Fig. 5. Measured interconnect S-parameters over 1 mm of interconnect.

indicate that the characteristic impedance of the lines changes by less than 5%. A segmented-ground transmission-line test structure was fabricated to compare the S-parameters with a regular bathtub transmission line. The measured S-parameters are compared in Fig. 5 and demonstrate that the loss of the segmented transmission line over 1 mm is around 3 dB and did not vary much between the segmented and normal transmission-line structure at 20 GHz. However, the measured return loss is increased by 3 dB at 20 GHz due to the severed ground plane.

#### B. Frequency Doubler

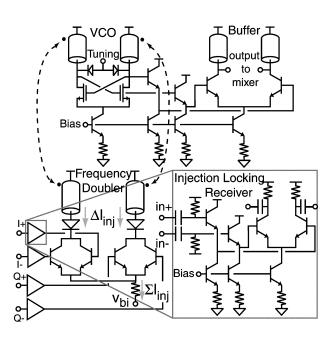

Since the injected signal is a subharmonic of the oscillator frequency, the injected frequency must be multiplied. At each oscillator, the I and Q injection signals are provided from the neighboring oscillators. Injection locking with both I and Q subharmonic signals increases the second harmonic power since  $\cos^2(\omega t) - \sin^2(\omega t) = \cos(2\omega t)$ . A circuit schematic for the frequency doubler and oscillator is shown in Fig. 6. The I/Q signals are picked up by a receiver that drives back-to-back bipolar devices. These transistors are biased below the forward active region to generate strong second harmonic content through rectification. Changing the bias voltage  $V_{\rm bi}$  allows control over the injected current at the second harmonic. The basic collector current dependence on the base–emitter diode voltage is

$$I_c = I_s (e^{V_{\rm be}/V_t} - 1)$$

(5)

Fig. 6. Injection locking and VCO topology.

where  $I_s$  is the saturation current,  $V_{be}$  is the base–emitter voltage, and  $V_T$  is the thermal voltage. If we assume that the bases are driven with a differential ac-coupled injection signal  $+/-V_{inj}\sin(\omega_{inj}t)$ , the sinusoidal dependence in the exponent is expressed through the series expansion

$$e^{\pm V_{\rm inj}\sin(\omega_{\rm inj}t)/V_T} \approx 1 \pm \frac{V_{\rm inj}}{V_T}\sin(\omega_{\rm inj}t) + \frac{1}{2}\frac{V_{\rm inj}^2}{V_T^2}\sin^2(\omega_{\rm inj}t) + \dots \quad (6)$$

Odd harmonic terms cancel when the injection current is added at the collector. One back-to-back transistor pair is driven by I, the other one by Q. Since the second harmonic remaining at the collector has a  $180^{\circ}$  phase difference ( $90^{\circ}$  multiplied by 2), the differential signal is generated for oscillator coupling. Consequently, the even harmonics remain in the current injected into the VCO tank circuit.

Additionally, resistor degeneration at the emitter of the bipolar transistors provides common mode rejection. Emitter degeneration is introduced with the resistor  $R_{inj}$  in the emitter and the base–emitter voltage changes to

$$V_{\rm be} = V_{\rm inj}\sin(\omega_{\rm inj}t) - R_{\rm inj}\sum I_{\rm inj}$$

(7)

where  $\Sigma I_{inj}$  is the common mode current. Recalculating (5), the differential collector current for the I and Q paths is

$$I_{\rm inj}^{+} = I_s \left( \left[ 2 + \left( \frac{V_{\rm inj}}{V_T} \right)^2 \cos^2(\omega_{\rm inj}t) \right] e^{\frac{-R_{\rm inj}\Sigma I_{\rm inj}}{V_T}} - 2 \right)$$

$$I_{\rm inj}^{-} = I_s \left( \left[ 2 + \left( \frac{V_{\rm inj}}{V_T} \right)^2 \sin^2(\omega_{\rm inj}t) \right] e^{\frac{-R_{\rm inj}\Sigma I_{\rm inj}}{V_T}} - 2 \right).$$

(8)

Finally, the difference of the expressions in (8) gives the desired injected signal

$$\Delta I_{\rm inj} = I_{\rm inj}^+ - I_{\rm inj}^- = I_s \left(\frac{V_{\rm inj}}{V_T}\right)^2 \cos(2\omega_{\rm inj}t) e^{\frac{-R_{\rm inj}\Sigma I_{\rm inj}}{V_T}}.$$

(9)

The injected current is twice the frequency of the I/Q signals and depends quadratically on the amplitude of the injected current. Adding the currents in (8) gives the total current through the emitter resistor

$$\Sigma I_{\rm inj} = I_{\rm inj}^+ + I_{\rm inj}^- = I_s \left( \left[ 4 + \left( \frac{V_{\rm inj}}{V_T} \right)^2 \right] e^{\frac{-R_{\rm inj}\Sigma I_{\rm inj}}{V_T}} - 4 \right).$$

(10)

The bias current is constant through the stage, but depends on the input power as the differential current did in (9). For small current levels, this transcendental equation can be approximated with a series for the exponential dependence on  $\Sigma I_{inj}$ . In this case,

$$\Sigma I_{\rm inj} \approx \frac{I_s (V_{\rm inj}/V_T)^2}{1 + \frac{I_s R_{\rm inj}}{V_T} \left(4 + (V_{\rm inj}/V_T)^2\right)}.$$

(11)

When the tail resistance is small,  $\Sigma I_{inj} \approx I_s V_{inj}^2 / V_T^2$ , and the total current depends on the power of the injected signals. For larger power levels, the total current saturates as  $\Sigma I_{inj} \approx V_T / R_{inj}$ . For a tail resistance of 20  $\Omega$ , this current is roughly 1.3 mA. Substituting (11) into (9), the differential mode current is

$$\Delta I_{\rm inj} = I_s \frac{V_{\rm inj}^2}{V_T^2} \cos(2\omega_{\rm inj}t) \frac{1 + \frac{4I_s R_{\rm inj}}{V_T}}{1 + \frac{I_s R_{\rm inj}}{V_T} \left(4 + \frac{V_{\rm inj}^2}{V_T^2}\right)}.$$

(12)

For large power levels, the total differential current saturates at

$$\Delta I_{\rm inj} = \left(\frac{V_T}{R_{\rm inj}} + 4I_s\right)\cos(2\omega_{\rm inj}t).$$

(13)

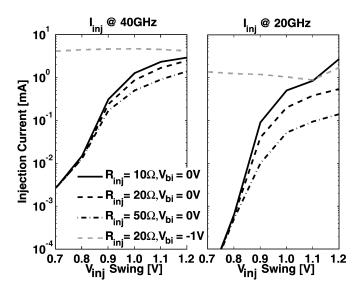

Hence, the differential injection current contains only energy at the twice the subharmonic and the amplitude of the injection signal is independent of the injected power level. For  $R_{\rm inj} < 26\Omega$ , the differential current swing should be greater than 1 mA. However, this equation only describes the current when no dc bias is provided across the base–emitter junction. In reality, the base–emitter voltage drop can also be fixed to increase the amount of injection current. An ADS simulation of the complete frequency doubling circuit is demonstrated in Fig. 7. The simulation is performed as a function of the injected subharmonic voltage are shown in the plot. The results provide a comparison for the amplitude of injected current at the subharmonic and carrier frequency.

Larger resistance provides more rejection of the subharmonic frequency, but limits the current injected into the tank. For this

Fig. 7. Current injected into the VCO at oscillator and subharmonic frequency.

design, we chose 20  $\Omega$  for the tail resistance as a tradeoff between the desired injection current and the rejection of the subharmonic frequency. Additionally, varying  $V_{\rm bi}$  at the tail resistance can provide a dc bias that puts the bipolar devices closer to the forward active region. This effect is plotted in Fig. 7 for  $V_{\rm bi} = -1.0$  V. Now the injection current depends weakly on the input subharmonic power and the injection current remains fixed at around 4 mA. However, the circuit also provides less rejection of the subharmonic energy.

Consequently, the subharmonic energy is efficiently converted to the oscillator frequency energy through the use of a frequency-doubling scheme. Now we turn our attention to the coupling of the injected signal into the VCO.

#### C. Injection-Locked Oscillator

Energy can be injected at many different points of the oscillator core. Injection-locked frequency dividers inject energy in the tail of a cross-coupled differential pair [24]. However, the tail is useful primarily for superharmonic injection locking because the emitter or source node of the differential pair is a virtual ground at the oscillator frequency. Alternatively, coupled oscillators have been proposed for quadrature generation [25], [26]. These schemes use a differential pair connected in parallel to the cross-coupled pair in the oscillator core to inject energy. The sizing of these devices and injection current control the coupling strength. This topology can be difficult to implement at millimeter-wave frequencies because the parasitic loading can result in a narrow or reduced the tuning range. Other papers have shown direct injection locking for quadrature generation through a separate differential stage that drives a ring oscillator [27].

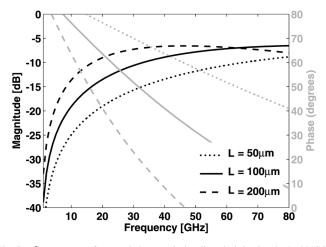

For this design, the frequency-doubler output is coupled into the VCO core with a coupled transmission line. The coupled transmission line is part of the VCO tank circuit to reduce the effect on the oscillator tuning range. Unfortunately, the coupled transmission line also limits coupling strength. S-parameter simulations of coupled transmission lines in this fabrication technology are shown in Fig. 8. The simulations are swept

Fig. 8. S-parameters for coupled transmission lines in injection-locked VCO.

for three different transmission-line lengths. At 40 GHz, the coupling between the injection-locking circuit and the VCO depends on the coupling length. The 50- $\mu$ m lines show a –15-dB coupling strength between the two circuits while the 200- $\mu$ m lines provide –7-dB coupling. Interestingly, the coupling reaches a maximum around this value and decreases at higher frequencies. In this case, the total inductance of the transmission-line tank of the VCO limited the coupled transmission-line section length to 100  $\mu$ m, providing –10-dB coupling. The lower coupling strength at 20 GHz provides additional rejection of the subharmonic energy. The coupled transmission line rejects the subharmonic frequency by –5 dB for the 100- $\mu$ m length compared to the oscillator harmonic frequency.

On the left-hand side of the schematic in Fig. 6, a simple cross-coupled nMOS VCO is shown. The oscillator tank consists of the combination of the transmission line and coupled transmission for inductance and varactor diodes. The tuning range of the VCO is over 4 GHz, approximately 10% of the carrier frequency. Notably, the oscillator self-mixing enhances the frequency tuning range at 60 GHz by the ratio of 3 : 2, and the tuning range should remain 10% of the oscillator frequency.

#### **IV. RESULTS**

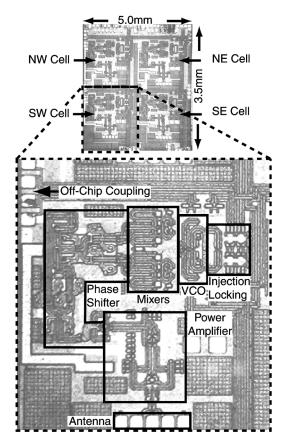

The coupled-oscillator array was constructed in IBM 8HP, a 130-nm SiGe process with bipolar and CMOS devices. The maximum  $f_T$  of the bipolar devices is 210 GHz. The array is shown in Fig. 9 and occupies an area of  $3.5 \text{ mm} \times 5 \text{ mm}$ . The wavelength of a 60-GHz signal determines the spacing between on-chip antennas. In air, the array spacing  $(\lambda/2)$  is roughly 2.5 mm. However, the array is intended to radiate through the die substrate where a silicon lens is used to absorb the radiated energy [2]. Consequently, the array spacing is designed for  $\varepsilon_r = 11.9$  and the array spacing is 0.7 mm. Unfortunately, the element spacing is too restrictive given geometry considerations for the on-chip antenna and the array spacing was chosen for 1.7 mm. This limits the beamsteering and causes undesirable sidelobes, but is still useful for the proof-of-concept. The enlarged version of one cell shows the antenna, which resides approximately 200  $\mu$ m from the five pads on the lower metal layers, as well as the power amplifier, DAC controlled phase

Fig. 9. Chip microphotograph for complete 60-GHz transmitter with a close-up view of one array element.

shifter, mixers, and injection-locked VCO. The antennas are placed on the lower metal layers to provide better power coupling to the silicon lens. The coupling interconnects run along the top and right-hand side of the cell to four pads that allow wire bonding to a neighboring dies. Each oscillator consumes 25 mA for the static frequency divider and 125 mA for the oscillator, frequency doubler, and coupling buffers. The current is increased by the use of the quadrature injection locking scheme since each oscillator drives four 50- $\Omega$  buffers.

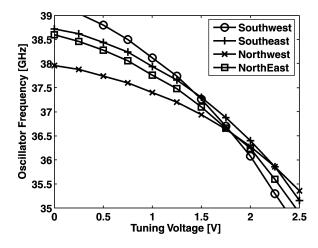

The VCO frequency varies between 35.5–39.5 GHz, falling 3.5 GHz below the desired range of 39–43 GHz. The tuning curve for each of the oscillators is shown in Fig. 10. The variation in the oscillator tuning range varies with location. The southern oscillators have a higher natural frequency than the northern oscillators. Additionally, the output power of these oscillators is approximately 3 dB lower. To prevent coupling between the antenna and large power supply connections on chip, the power supply was provided along an axis perpendicular to the on-chip antennas in the microphotograph in Fig. 9. Consequently, both northern oscillators are located closer to the power supply pads and the resulting drop in power seems most likely due to voltage drop along the supply lines. As the oscillators are tuned together, the locking range determines the usable oscillator frequency range.

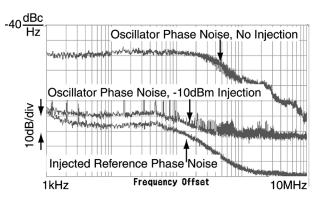

To characterize the performance of the coupled-oscillator array, a VCO test structure is initially measured under injection-locking conditions. The phase noise of the free-running oscillator, as well as the locked oscillator is demonstrated in

Fig. 10. Tuning range for each oscillator in  $2 \times 2$  array. The difference between the natural frequencies of each oscillator is greatest near the highest frequencies.

Fig. 11. Phase noise of reference, injection-locked oscillator, and unlocked oscillator.

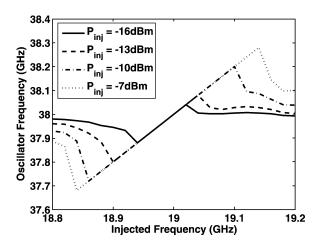

Fig. 12. Locking range for the VCO as a function of injected power.

Fig. 13. Testing scheme for the coupled-oscillator array.

Fig. 11. The locked oscillator phase noise tracks the injected reference with 6-dB higher phase noise. The injected signal is at 20 GHz and the phase noise is measured at 40 GHz. Consequently, there is a 6-dB penalty in the phase noise of the locked on-chip oscillator. At 1-MHz offset, the phase noise of the locked oscillator is -112 dBc/Hz. The injection-locking characteristics are measured as a function of injection power. In Fig. 12, the carrier frequency is measured as a function of the injected subharmonic frequency. At  $P_{inj} = -16$  dBm, the locking range is around 60 MHz and increases to 320 MHz at  $P_{inj} = -7$  dBm. To verify these locking-range results, we compare the expression for the locking range to these measured results. If the locking range is 320 MHz and the tank Q is around 10 at 40 GHz,

$$I_{\rm inj} = I_{\rm osc} \frac{2Q\Delta\omega_m}{\omega_o} = 10 \text{ mA} \frac{2 \cdot 10 \cdot 320 \text{ MHz}}{40 \text{ GHz}} = 1.6 \text{ mA.}$$

(14)

Comparing this to our simulations in Fig. 7 provides agreement about anticipated injection current levels.

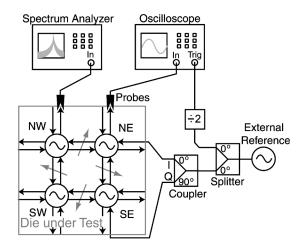

In Fig. 13, the testing scheme for the coupled oscillator is illustrated. The external reference drives a 20-GHz signal through a power splitter and an I/Q coupler. The second signal from the power splitter is divided down to 10 GHz and used to trigger an Agilent 81600C oscilloscope. The I/Q signals from the coupler are delay matched to externally lock the coupled-oscillator array. The I signal is fed to the East edge and the Q signal is fed to the South edge. Additionally, the locking is controlled on-chip through the bias voltage of the frequency-doubling circuit, as described in Section III. For testing the  $2 \times 2$  array, each oscillator can be probed with the high-speed sampling head in the oscilloscope or the spectrum analyzer. The oscillator behavior is studied by observing the 20-GHz injection-locking signal of the oscillator.

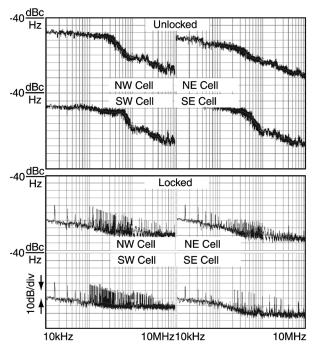

In Fig. 14, the phase noise of the  $2 \times 2$  coupled-oscillator array structure is shown with and without injection locking. In this case, the average phase noise of each oscillator is around -93 dBc/Hz at 1-MHz offset. Next, a -10-dBm external reference is injected at the northeast and southeast oscillators. The injection current, controlled with  $V_{bi}$ , was set to draw 8 mA per cell. The oscillator phase noise was consecutively measured without changing the operating conditions. The phase noise of the injection-locked VCOs is around -114 dBc/ Hz at 1-MHz offset. The locking range for the array under these conditions is approximately 200 MHz. The operation of the locked array is limited by the natural frequency and power variations for each oscillator. This also affects the phase noise of each oscillator in

Fig. 14. Phase noise of each oscillator in  $2 \times 2$  single chip array: (*top*) without and (*bottom*) with injection locking.

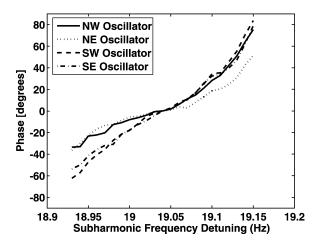

Fig. 15. Phase of each oscillator in array across locking range.

the array. This supply and bias mismatch dominates the process and temperature variations that might occur on-chip.

The phase of each oscillator can also be measured at 20 GHz with a high-speed sampling scope. The externally injected signal is used to trigger the high-speed scope. The phase progression of each oscillator is demonstrated in Fig. 15 and is normalized to zero to provide relative comparison of the phase. The maximum oscillator phase variation is at most  $-60^{\circ}$  to  $80^{\circ}$  over the 200-MHz locking range. This locking range is measured at the subharmonic frequency, but the phase variation is calculated for the actual carrier frequency. Voltage variations strongly influence the locking range. Note that the southern oscillator current. Any phase offset between the oscillators can be compensated with the DAC controlled mixer that provides phase shifting.

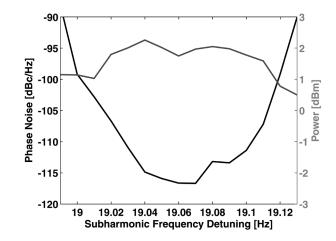

Fig. 16. Phase noise of northwest oscillator as a function of frequency detuning.

Fig. 17. Phase noise of oscillators across a  $1 \times 4$  array with two different dies.

Additionally, the frequency detuning between the reference and the oscillator was scanned to measure the change in the phase noise in Fig. 16. As demonstrated in [18], the phase noise changes as a function of the frequency detuning depending on the frequency offset. The curve qualitatively agrees with those predictions as the phase noise increases near the edges of the locking range. To achieve the best phase-noise performance across a grid of oscillators, the frequency detuning of all the oscillators should be minimized.

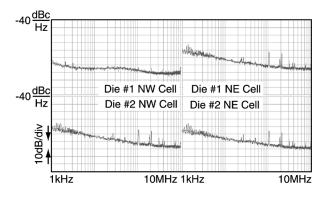

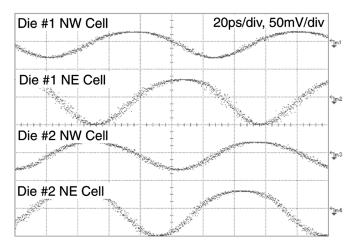

Finally, a  $1 \times 4$  oscillator array is measured in Fig. 17 with an external injection signal of -10 dBm at the NE oscillator of die #1. The testing scheme described in Fig. 13 is altered to include a second die. The coupling ports of the two chips are wire bonded together and the southern oscillators on both chips are turned off. As before, the spectrum analyzer and oscilloscope can probe each of the oscillator injection locking ports to measure the array behavior. The locking range under these conditions is roughly 60 MHz and is reduced partly because only the in-phase signals are used to injection lock the array. The phase noise of the locked oscillator closest to the external reference is -110 dBc/Hz at a 1-MHz offset. Each consecutive oscillator has phase noise of -105, -107, and -108 dBc/Hz. The phase noise would ideally increase across the array. Instead, the irregular shift in phase noise may result from the natural frequency detuning between the neighboring oscillators. Nonetheless, the

Fig. 18. Oscilloscope waveforms for 20-GHz injection signals across  $1 \times 4$  array.

low phase noise across the two chips is encouraging for demonstrating larger arrays by locking on-chip oscillators to off-chip reference signals.

The phases of each oscillator in the  $1 \times 4$  array are shown in Fig. 18. The phase shift introduced between the two dies is nearly 180°, while the phase difference between the on-chip oscillators is smaller. This is presumably related to the difference in the injection strength between chips, as opposed to between oscillators on the same chip. This degradation in the injection frequency can also result in the lower locking range of the  $1 \times 4$ array. The impedance of a short (0.2 mm) wire bond can be estimated as  $2\pi(0.2 \text{ nH} \cdot 20 \text{ GHz}) \approx 25 \Omega$  and induces mismatch in the interconnect between two dies.

## V. CONCLUSION

This paper has described the implementation of a coupled-oscillator array integrated in an SiGe process for millimeter-wave applications. The coupled oscillator employs quadrature subharmonic injection locking to couple neighboring phased-array elements both on-chip and between chips with wire-bond interconnects. Measurements of the oscillator array demonstrate reduced phase noise when locked to an external reference. The locking range was measured to be 200 MHz for the oscillators on a single die and is limited by the process and voltage variations that exist over the large die area.

#### ACKNOWLEDGMENT

The authors acknowledge the support of the Defense Advanced Research Projects Agency (DARPA) Trusted Foundries Program for access to the 8HP technology. Additionally, we thank the Rogers Corporation, Rogers, CT, for the generous donation of the duroid.

#### REFERENCES

S. Reynolds *et al.*, "60 GHz transceiver circuits in SiGe bipolar technology," in *IEEE Int. Solid-State Circuits Conf.*, Feb. 2004, pp. 442–444.

- [2] A. Babakhani *et al.*, "77 GHz four element phased array receiver with on-chip dipole antennas in silicon," in *IEEE Int. Solid-State Circuits Conf.*, Feb. 2006, pp. 180–181.

- [3] B. Razavi, "A 60 GHz direct-conversion receiver," in *IEEE Int. Solid-State Circuits Conf.*, Feb. 2005, pp. 400–402.

- [4] X. Guan et al., "A fully integrated 24-GHz eight element phased-array receiver in silicon," *IEEE J. Solid-State Circuits*, vol. 39, no. 12, pp. 2311–2320, Dec. 2004.

- [5] J. Buckwalter *et al.*, "Quadrature subharmonic coupled oscillators for a 60 GHz SiGe scalable phased array," presented at the IEEE MTT-S Int. Microw. Symp., Jun. 2006.

- [6] H. Hashemi *et al.*, "A 24-GHz SiGe phased array receiver-LO phase shifting approach," *IEEE Trans. Microw. Theory Tech.*, vol. 53, no. 2, pp. 614–626, Feb. 2005.

- [7] J. J. Lynch and R. A. York, "A mode-locked array of coupled phaselocked loops," *IEEE Microw. Guided Wave Lett.*, vol. 5, no. 7, pp. 213–215, Jul. 1995.

- [8] J. F. Buckwalter, T. H. Heath, and R. A. York, "Synchronization design of a coupled phase-locked loop," *IEEE Trans. Microw. Theory Tech.*, vol. 51, no. 3, pp. 952–960, Mar. 2003.

- [9] A. Hajimiri et al., "Integrated phased-array systems in silicon," Proc. IEEE, vol. 93, no. 9, pp. 1637–1655, Sep. 2005.

- [10] R. Adler, "A study of locking behavior in oscillators," *Proc. IEEE*, vol. 61, no. 10, pp. 1380–1385, Oct. 1973.

- [11] K. Kurokawa, "Injection locking of microwave solid-state oscillators," *Proc. IEEE*, vol. 61, no. 10, pp. 1386–1410, Oct. 1973.

- [12] K. D. Stephan, "Inter-injection-locked oscillators for power combining and phased arrays," *IEEE Trans. Microw. Theory Tech.*, vol. 34, no. 10, pp. 1017–1025, Oct. 1986.

- [13] R. A. York and R. C. Compton, "Measurement and modelling of radiative coupling in oscillator arrays," *IEEE Trans. Microw. Theory Tech.*, vol. 34, no. 3, pp. 438–444, Mar. 1993.

- [14] R. A. York, P. Liao, and J. J. Lynch, "Oscillator array dynamics with broadband *N*-port coupling networks," *IEEE Trans. Microw. Theory Tech.*, vol. 34, no. 3, pp. 438–444, Mar. 1993.

- [15] R. A. York and T. Itoh, "Injection and phase-locking techniques for beam control," *IEEE Trans. Microw. Theory Tech.*, vol. 46, no. 11, pp. 1920–1929, Nov. 1998.

- [16] R. J. Pogorzelski, P. F. Maccarini, and R. A. York, "Continuum modeling of the dynamics of externally injection-locked coupled oscillator arrays," *IEEE Trans. Microw. Theory Tech.*, vol. 47, no. 4, pp. 471–478, Apr. 1999.

- [17] R. J. Pogorzelski and F. F. Chiha, "A demonstration of the coupled oscillator based agile beam receiver concept," *IEEE Trans. Antennas Propag.*, vol. 53, no. 11, pp. 3584–3588, Nov. 2005.

- [18] H.-C. Chiang *et al.*, "Phase noise in externally injection-locked oscillator arrays," *IEEE Trans. Microw. Theory Tech.*, vol. 45, no. 11, pp. 2035–2042, Nov. 1997.

- [19] K. D. Stephan and S. L. Young, "Mode stability of radiation-coupled interinjection-locked oscillators for integrated phased arrays," *IEEE Trans. Microw. Theory Tech.*, vol. 36, no. 5, pp. 921–924, May 1988.

- [20] J. J. Lynch and R. A. York, "Stability of mode-locked states of coupled oscillators," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 42, no. 8, pp. 413–418, Aug. 1995.

- [21] B. Razavi, "A study of injection locking and pulling in oscillators," *IEEE J. Solid-State Circuits*, vol. 39, no. 9, pp. 1415–1424, Sep. 2004.

- [22] A. Komijani, A. Natarajan, and A. Hajimiri, "A 24 GHz, +14.5 dBm fully integrated power amplifier in 0.18 μm CMOS," *IEEE J. Solid-State Circuits*, vol. 40, no. 9, pp. 1901–1908, Sep. 2005.

- [23] A. Komijani and A. Hajimiri, "A wideband 77 GHz, 17.5 dBm fully integrated power amplifier in silicon," *IEEE J. Solid-State Circuits*, vol. 41, no. 8, pp. 1749–1756, Aug. 2006.

- [24] H. R. Rategh and T. H. Lee, "Super-harmonic injection-locked frequency dividers," *IEEE J. Solid-State Circuits*, vol. 34, no. 6, pp. 813–821, Jun. 1999.

- [25] R. Aparicio and A. Hajimiri, "A noise-shifting differential Colpitts VCO," *IEEE J. Solid-State Circuits*, vol. 37, no. 12, pp. 1728–1736, Dec. 2002.

- [26] A. Mazzanti, F. Svelto, and P. Andreani, "On the amplitude and phase errors of quadrature *LC*-tank CMOS oscillators," *IEEE J. Solid-State Circuits*, vol. 41, no. 6, pp. 1305–1313, Jun. 2006.

- [27] P. Kinget *et al.*, "An injection-locking scheme for precise quadrature generation," *IEEE J. Solid-State Circuits*, vol. 37, no. 7, pp. 845–851, Jul. 2002.

James F. Buckwalter (S'01–M'06) received the B.S. degree in electrical engineering from the California Institute of Technology, Pasadena, in 1999, the M.S. degree in electrical engineering from the University of California at Santa Barbara, in 2001, and is currently with the California Institute of Technology working toward the Ph.D. degree in electrical engineering.

From 1999 to 2000, he was a Research Scientist with Telcordia Technologies, where he was involved with rate-agile burst-mode electronics

under a next-generation Internet Defense Advanced Research Projects Agency (DARPA) project. During Summer 2004, he was with the IBM T. J. Watson Research Center, Yorktown Heights, NY, where he developed new equalization techniques for high-speed serial links. In 2006, he joined Luxtera, Carlsbad, CA, where he developed high-speed circuits for optical interconnects. In July 2006, he joined the faculty of the University of California at San Diego, La Jolla, where he is currently an Assistant Professor of electrical engineering. His research interests are high-speed serial links, mixed-signal circuit design, and microwave and millimeter-wave integrated circuits.

Dr. Buckwalter was the recipient of the 2003 Analog Devices Outstanding Student Designer Award and a 2004 IBM Ph.D. Fellowship.

**Aydin Babakhani** (S'03) received the B.S. degree in electronics engineering from the Sharif University of Technology, Tehran, Iran, in 2003, the M.S. degree in electrical engineering from California Institute of Technology, Pasadena, in 2005, and is currently working toward the Ph.D. degree at the California Institute of Technology.

Mr. Babakhani is the vice chair of the IEEE Microwave Theory and Techniques Society (IEEE MTT-S) Metro LA/SFV joint sections MTT-S Chapter 17.1. He was the recipient of the Grand

Prize of the 2006 Stanford–Berkeley–California Institute of Technology Innovators Challenge, the 2005 International Solid-State Circuits Conference Analog Devices Inc. Outstanding Student Designer Award, and the 2003 California Institute of Technology Special Institute Fellowship and Atwood Fellowship. He was also the 1998 Gold Medal recipient of the National Physics Competition and the 1999 Gold Medal recipient of the 30th International Physics Olympiad, Padova, Italy.

Abbas Komijani (S'98–M'99) received the B.S. and M.S. degrees in electronics engineering from the Sharif University of Technology, Tehran, Iran, in 1995 and 1997, respectively, and is currently working toward the Ph.D. degree at the California Institute of Technology, Pasadena.

From 1997 to 1999, he was a Senior Design Engineer with Emad Semiconductors, Tehran, Iran, where he was involved with CMOS chipsets for voiceband applications. From 1999 to 2000, he was a Senior Design Engineer with Valence Semiconductors, Irvine, CA, where he was involved with data converters for voice over Internet Protocol (VoIP) applications. His research interests include high-frequency power amplifiers, wireless transceivers, phased-array architectures, and delta–sigma data converters.

Mr. Komijani was the recipient of the 1991 Silver Medal of the National Mathematics Olympiad, the 2000 California Institute of Technology Atwood Fellowship, the 2004 IEEE Custom Integrated Circuits Conference (CICC) Best Student Paper Award, the 2005 Analog Devices Outstanding Student Designer Award, the 2006 Grand Prize of the Stanford–Berkeley–California Institute of Technology Innovators' Challenge, and the 2006 Outstanding Ph.D. Student Award presented by the Association of Professors and Scholars of Iranian Heritage (APSIH).

Ali Hajimiri (S'95–M'99) received the B.S. degree in electronics engineering from the Sharif University of Technology, Tehran, Iran, in 1994, and the M.S. and Ph.D. degrees in electrical engineering from the Stanford University, Stanford, CA, in 1996 and 1998, respectively.

From 1993 to 1994, he was a Design Engineer with Philips Semiconductors, where he was involved with a BiCMOS chipset for global system for mobile communications (GSM) and cellular units. In 1995, he was with Sun Microsystems,

where he was involved with the UltraSPARC microprocessor's cache RAM design methodology. During Summer 1997, he was with Lucent Technologies (Bell Laboratories), Murray Hill, NJ, where he investigated low-phase-noise integrated oscillators. In 1998, he joined the faculty of the California Institute of Technology, Pasadena, where he is currently an Associate Professor of electrical engineering and the Director of the Microelectronics Laboratory. He is a cofounder of Axiom Microdevices Inc. He authored *The Design of Low Noise Oscillators* (Kluwer, 1999). He holds several U.S. and European patents. He is on the Guest Editorial Board of the *Transactions of the Institute of Electronics, Information and Communication Engineers of Japan* (IEICE). His research interests are high-speed and RF integrated circuits.

Dr. Hajimiri is a Fellow of the Okawa Foundation. He is an associate editor of the IEEE JOURNAL OF SOLID-STATE CIRCUITS. He is a member of the Technical Program Committee of the International Solid-State Circuits Conference (ISSCC). He has also served as an associate editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-PART II: FUNDAMENTAL THEORY AND APPLICATIONS. He is a member of the Technical Program Committees of the International Conference on Computer Aided Design (ICCAD). He was a guest editor of the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES. He was selected to the top 100 innovators (TR100) list in 2004. He was a recipient of the Teaching and Mentoring Award presented by the California Institute of Technology. He was the Gold Medal winner of the National Physics Competition and the Bronze Medal winner of the 21st International Physics Olympiad, Groningen, The Netherlands. He was a corecipient of the International Solid-State Circuits Conference (ISSCC) 1998 Jack Kilby Outstanding Paper Award, two-time corecipient of CICC's Best Paper Award, and a three-time recipient of the IBM Faculty Partnership Award. as well as the National Science Foundation (NSF) CAREER Award.