In this tutorial you are going to verify the inverter layout drawn in the previous tutorial using the Design Rule Checker (DRC). You should have basic understanding of the layout rules from lecture, but if you need a refresher, the links below will take you to the relevant section of the mosis web site. Be sure to use the SUBM version of the SCMOS SCN3M.

For those who want to know all the layers, please go to this url.Let's start verifying the layout we did in the last tutorial.

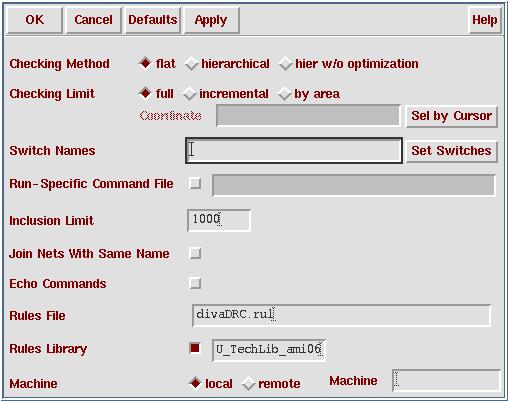

Now we are going to check if there are any DRC errors in the layout. The layout DRC rules are summarised by the design rules shown above. If you know what could be wrong in the layout, you can try to fix it/them and verify your modified layout by DRC. If not, let's go on to verification.

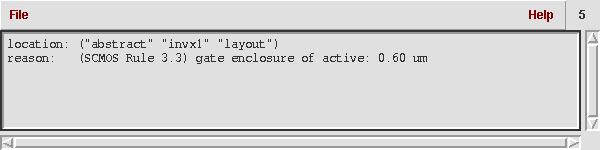

It takes a while to check all the DRC rules defined in the technology files. You can see those rules run across CIW very fast. After DRC checking is done, DRC errors will be highlighted in white on the Virtuoso Editing window. There is one error in this case. To see what the errors are

We have to fix the errors before we go any further. Press the F4 key to change the (F)Select:1 at the top center of the layout window to (P)Select:1 Now instead of selecting entire (full) shapes, you can select and adjust partial shapes. Select just the lower side of the poly. Move the mouse around until the cursor becomes an arrow pointing to a line. When this happens, you can left click and drag to adjust the shape of the rectangle. Make the poly region line up with the bottom of the larger nselect region

You need to do DRC again to make sure the error is fixed. You should find no error this time. Save your design before you go any further. Your layout view should look like this:

Comment: Plotting doesn't work well for Sun workstations. Therefore you need to plot to a postscript file first, then sent the postscript file to printer.